라즈베리파이 5는 단순한 소형 컴퓨터를 넘어서, 하드웨어와 소프트웨어를 연결하는 강력한 플랫폼으로 자리 잡고 있습니다. 그 중심에는 바로 GPIO(General Purpose Input/Output), 즉 범용 입출력 핀이 있습니다. 라즈베리파이 5의 40핀 GPIO 헤더는 작은 보드 위에 규칙적으로 배열된 핀들로, 각 핀은 디지털 신호를 읽거나 쓰고, 다양한 전자 장치나 센서, 모듈과의 직접적인 통신을 가능하게 만듭니다.

GPIO의 매력은 단순함에서 출발합니다. 특정 핀에 전압을 주면 “1”, 전압이 없으면 “0”으로 읽히며, 반대로 원하는 핀에 신호를 주어 LED를 켜거나 모터를 돌리는 등의 출력을 제어할 수 있습니다. 이 간단한 논리가 프로그래밍과 결합될 때, 우리는 단순한 버튼에서부터 복잡한 로봇 제어, IoT(사물인터넷) 기기, 스마트 홈 프로젝트까지 수많은 창의적인 작업을 할 수 있게 됩니다.

특히 라즈베리파이 5의 GPIO는 이전 세대에 비해 더욱 안정적이고 고성능으로 업그레이드되었으며, SPI, I²C, UART 같은 다양한 통신 프로토콜도 지원합니다. 이는 단순한 입출력 제어를 넘어서, 복잡한 외부 장치와의 통합까지도 가능하게 한다는 점에서 매우 중요합니다.

이 글에서는 라즈베리파이 5의 40핀 GPIO 헤더가 가진 각 핀의 기능과 역할을 하나하나 뜯어보고, 초보자도 이해할 수 있도록 구조적이고 명확하게 설명해 보겠습니다. GPIO의 기본 개념과 중요성을 이해하고 나면, 단순한 취미를 넘어, 진정한 디지털 제작자의 길로 나아가는 문이 열릴 것입니다. 이 여정을 함께 시작해봅시다.

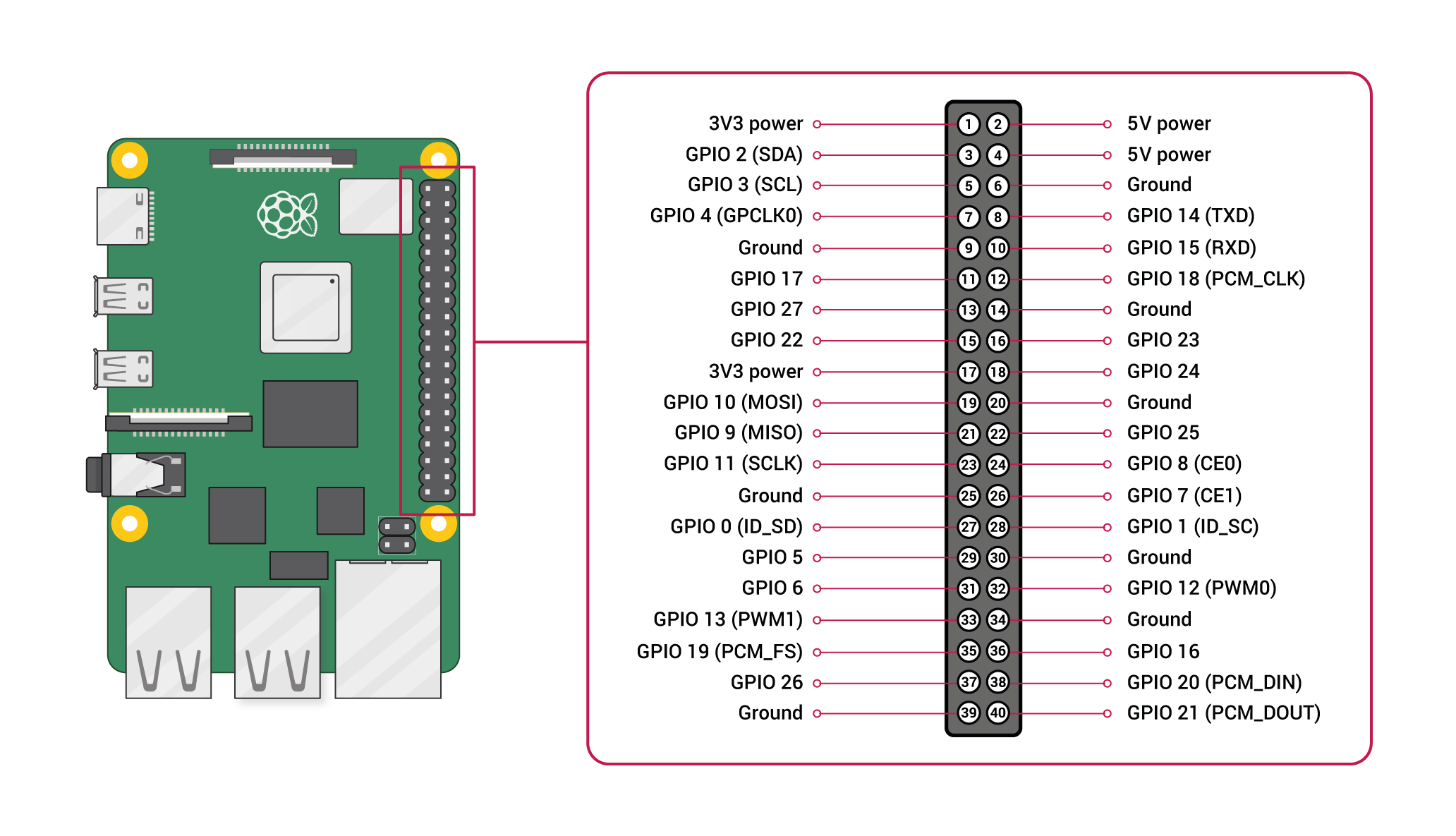

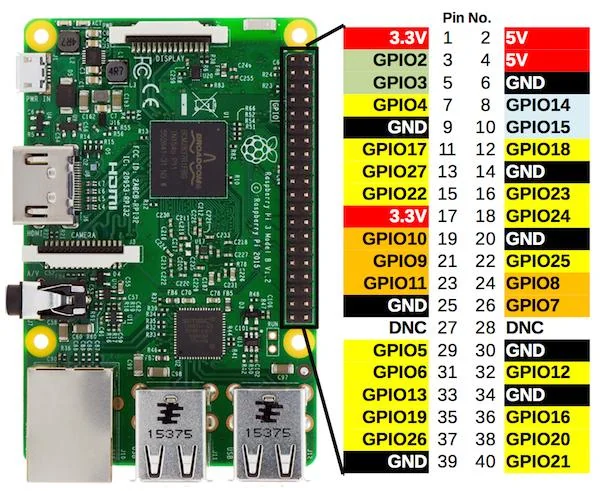

라즈베리파이5 GPIO 40핀 헤더 GPIO 자세히 살펴보기

이 그래픽은 라즈베리파이 5의 연결 핀아웃을 보여주며, 기본 장치 트리 오버레이가 있는 기본 구성입니다. 기본 구성은 대부분 아래 표의 'F1'과 일치합니다.

다이어그램은 변경될 수 있으며 아직 출시되지 않은 제품을 참조하므로 '초안' 버전으로 간주될 수 있습니다.

다이어그램에서 다루는 헤더는 다음과 같습니다:

- J8 GPIO 헤더, 기본 40핀 gpio.

- J14 PoE

- J2 전원 스위치(공식적으로 확인되지 않음, 대신 RTC 배터리와 관련이 있을 수 있음)

- J7 컴포지트 비디오(더 이상 오디오 잭에 없음)

- J17 팬 헤더(PWM 제어 및 속도 감지 가능)

이에 대한 무료 문서는 다음 RP1 문서입니다: RP1 데이터시트 - 주변 장치 컨트롤러 데이터시트 초안, 이제 Pi의 입력/출력이 자체 GPIO가 있는 RP1에서 처리됩니다.

다음은 해당 문서에서 발췌한 내용입니다:

RP1에는 28개의 다기능 범용 입력/출력 핀이 있어 표준 라즈베리파이 40핀을 구현하는 데 사용할 수 있습니다. GPIO 커넥터를 구현할 수 있습니다. GPIO 핀은 RP1에 전원이 공급되는 경우 최대 5V, 전원이 공급되지 않는 경우 3.63V를 견딜 수 있습니다.

핀은 단일 전기 뱅크(VDDIO0)에 있습니다. GPIO 뱅크(IO_BANK0)는 1.8V 또는 3.3V에서 전원을 공급받을 수 있습니다. 인터페이스 타이밍은 3.3V로 지정되어 있습니다. 각 핀은 소프트웨어 또는 기타 여러 기능 블록을 통해 직접 제어할 수 있습니다.

뱅크는 다음과 같은 기능을 지원합니다:

- 5 × UART - 6 × SPI - 4 × I2C

- 2 × I2S - 1× 클록 생산자 인스턴스, 1× 클록 소비자 인스턴스.

- RIO 등록된 IO 인터페이스

- 24비트 DPI 출력

- 4채널 PWM 출력

- AUDIO_OUT

- 스테레오 PWM 오디오 출력

- GPCLK - 범용 클럭 입력 및 출력

- 4비트 인터페이스가 있는 eMMC/SDIO 버스

- 핀 레벨 또는 엣지 트랜지션에서 인터럽트 생성

기능 블록과 GPIO 핀의 위치는 라즈베리 파이 4 모델 B의 40핀 헤더에 있는 사용자 대면 기능과 일치하도록 선택되었습니다. 핀 헤더의 사용자 대면 기능과 일치하도록 선택되었습니다. -- 이전 라즈베리 파이 모델과 마찬가지로 GPIO는 여러 기능을 가질 수 있으며, 다음은 각 GPIO의 다양한 기능에 대한 표입니다.

| Function | |||||||||

| GPIO | F1 | F2 | F3 | F4 | F5 | F6 | F7 | F8 | F9 |

| 0 | SPI0_SIO[3] | DPI_PCLK | UART1_TX | I2C0_SDA | SYS_RIO[0] | PROC_RIO[0] | PIO[0] | SPI2_CSn[0] | |

| 1 | SPI0_SIO[2] | DPI_DE | UART1_RX | I2C0_SCL | SYS_RIO[1] | PROC_RIO[1] | PIO[1] | SPI2_SIO[1] | |

| 2 | SPI0_CSn[3] | DPI_VSYNC | UART1_CTS | I2C1_SDA | UART0_IR_RX | SYS_RIO[2] | PROC_RIO[2] | PIO[2] | SPI2_SIO[0] |

| 3 | SPI0_CSn[2] | DPI_HSYNC | UART1_RTS | I2C1_SCL | UART0_IR_TX | SYS_RIO[3] | PROC_RIO[3] | PIO[3] | SPI2_SCLK |

| 4 | GPCLK[0] | DPI_D[0] | UART2_TX | I2C2_SDA | UART0_RI | SYS_RIO[4] | PROC_RIO[4] | PIO[4] | SPI3_CSn[0] |

| 5 | GPCLK[1] | DPI_D[1] | UART2_RX | I2C2_SCL | UART0_DTR | SYS_RIO[5] | PROC_RIO[5] | PIO[5] | SPI3_SIO[1] |

| 6 | GPCLK[2] | DPI_D[2] | UART2_CTS | I2C3_SDA | UART0_DCD | SYS_RIO[6] | PROC_RIO[6] | PIO[6] | SPI3_SIO[0] |

| 7 | SPI0_CSn[1] | DPI_D[3] | UART2_RTS | I2C3_SCL | UART0_DSR | SYS_RIO[7] | PROC_RIO[7] | PIO[7] | SPI3_SCLK |

| 8 | SPI0_CSn[0] | DPI_D[4] | UART3_TX | I2C0_SDA | SYS_RIO[8] | PROC_RIO[8] | PIO[8] | SPI4_CSn[0] | |

| 9 | SPI0_SIO[1] | DPI_D[5] | UART3_RX | I2C0_SCL | SYS_RIO[9] | PROC_RIO[9] | PIO[9] | SPI4_SIO[0] | |

| 10 | SPI0_SIO[0] | DPI_D[6] | UART3_CTS | I2C1_SDA | SYS_RIO[10] | PROC_RIO[10] | PIO[10] | SPI4_SIO[1] | |

| 11 | SPI0_SCLK | DPI_D[7] | UART3_RTS | I2C1_SCL | SYS_RIO[11] | PROC_RIO[11] | PIO[11] | SPI4_SCLK | |

| 12 | PWM0[0] | DPI_D[8] | UART4_TX | I2C2_SDA | AUDIO_OUT_L | SYS_RIO[12] | PROC_RIO[12] | PIO[12] | SPI5_CSn[0] |

| 13 | PWM0[1] | DPI_D[9] | UART4_RX | I2C2_SCL | AUDIO_OUT_R | SYS_RIO[13] | PROC_RIO[13] | PIO[13] | SPI5_SIO[1] |

| 14 | PWM0[2] | DPI_D[10] | UART4_CTS | I2C3_SDA | UART0_TX | SYS_RIO[14] | PROC_RIO[14] | PIO[14] | SPI5_SIO[0] |

| 15 | PWM0[3] | DPI_D[11] | UART4_RTS | I2C3_SCL | UART0_RX | SYS_RIO[15] | PROC_RIO[15] | PIO[15] | SPI5_SCLK |

| 16 | SPI1_CSn[2] | DPI_D[12] | MIPI0_DSI_TE | UART0_CTS | SYS_RIO[16] | PROC_RIO[16] | PIO[16] | ||

| 17 | SPI1_CSn[1] | DPI_D[13] | MIPI1_DSI_TE | UART0_RTS | SYS_RIO[17] | PROC_RIO[17] | PIO[17] | ||

| 18 | SPI1_CSn[0] | DPI_D[14] | I2S0_SCLK | PWM0[2] | I2S1_SCLK | SYS_RIO[18] | PROC_RIO[18] | PIO[18] | GPCLK[1] |

| 19 | SPI1_SIO[1] | DPI_D[15] | I2S0_WS | PWM0[3] | I2S1_WS | SYS_RIO[19] | PROC_RIO[19] | PIO[19] | |

| 20 | SPI1_SIO[0] | DPI_D[16] | I2S0_SDI[0] | GPCLK[0] | I2S1_SDI[0] | SYS_RIO[20] | PROC_RIO[20] | PIO[20] | |

| 21 | SPI1_SCLK | DPI_D[17] | I2S0_SDO[0] | GPCLK[1] | I2S1_SDO[0] | SYS_RIO[21] | PROC_RIO[21] | PIO[21] | |

| 22 | SDIO0_CLK | DPI_D[18] | I2S0_SDI[1] | I2C3_SDA | I2S1_SDI[1] | SYS_RIO[22] | PROC_RIO[22] | PIO[22] | |

| 23 | SDIO0_CMD | DPI_D[19] | I2S0_SDO[1] | I2C3_SCL | I2S1_SDO[1] | SYS_RIO[23] | PROC_RIO[23] | PIO[23] | |

| 24 | SDIO0_DAT[0] | DPI_D[20] | I2S0_SDI[2] | I2S1_SDI[2] | SYS_RIO[24] | PROC_RIO[24] | PIO[24] | SPI2_CSn[1] | |

| 25 | SDIO0_DAT[1] | DPI_D[21] | I2S0_SDO[2] | AUDIO_IN_CLK | I2S1_SDO[2] | SYS_RIO[25] | PROC_RIO[25] | PIO[25] | SPI3_CSn[1] |

| 26 | SDIO0_DAT[2] | DPI_D[22] | I2S0_SDI[3] | AUDIO_IN_DAT0 | I2S1_SDI[3] | SYS_RIO[26] | PROC_RIO[26] | PIO[26] | SPI5_CSn[1] |

| 27 | SDIO0_DAT[3] | DPI_D[23] | I2S0_SDO[3] | AUDIO_IN_DAT1 | I2S1_SDO[3] | SYS_RIO[27] | PROC_RIO[27] | PIO[27] | SPI1_CSn[1] |

각 GPIO는 한 번에 하나의 기능만 선택할 수 있습니다. 마찬가지로, 각 주변 장치 입력(예: I2C3_SCL)은 한 번에 하나의 GPIO에서만 선택해야 합니다. 동일한 주변기기 입력이 여러 GPIO에 연결된 경우 주변기기는 이러한 GPIO 입력의 논리적 OR을 인식합니다. 이 목록에 명명된 함수가 없는 함수 선택은 예약되어 있습니다.

문서 참고는 엘리먼트14

'라즈베리파이 5' 카테고리의 다른 글

| "Unable to determine board revision from /proc/cpuinfo" error after kernel 6.1 update (1) | 2024.05.22 |

|---|---|

| 라즈베리 파이 애호가 퀴즈 II (1) | 2024.05.14 |

| 라즈베리 파이5에 관해 얼마나 알고 계십니까? - 파이 애호가 퀴즈 III (0) | 2024.05.10 |

| 라즈베리 파이 5 FAQ - 라즈베리 파이 5에 관해 자주 묻는 질문 (0) | 2024.05.09 |

| raspberry pi5 GPIO 제어 WiringPi 설치 방법 (0) | 2024.05.07 |

| 라즈베리파이5 PCIe 활성화 방법 (1) | 2024.05.07 |

| 라즈베리파이 사용할 때 필요한 3가지 무료 프로그램 (0) | 2024.05.06 |

| 라즈베리파이에서 반드시 알아야 할 것들 (1) | 2024.05.03 |

취업, 창업의 막막함, 외주 관리, 제품 부재!

당신의 고민은 무엇입니까? 현실과 동떨어진 교육, 실패만 반복하는 외주 계약,

아이디어는 있지만 구현할 기술이 없는 막막함.

우리는 알고 있습니다. 문제의 원인은 '명확한 학습, 실전 경험과 신뢰할 수 있는 기술력의 부재'에서 시작됩니다.

이제 고민을 멈추고, 캐어랩을 만나세요!

코딩(펌웨어), 전자부품과 디지털 회로설계, PCB 설계 제작, 고객(시장/수출) 발굴과 마케팅 전략으로 당신을 지원합니다.

제품 설계의 고수는 성공이 만든 게 아니라 실패가 만듭니다. 아이디어를 양산 가능한 제품으로!

귀사의 제품을 만드세요. 교육과 개발 실적으로 신뢰할 수 있는 파트너를 확보하세요.

캐어랩